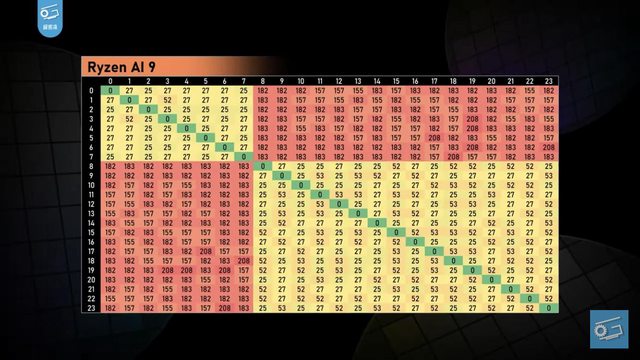

推 canandmap: 推解說,所以延遲高的原因看起來似乎 36.228.160.137 07/31 11:20

→ canandmap: 就是L3不夠+IF頻寬不足,導致這樣的結 36.228.160.137 07/31 11:21

→ canandmap: 果發生 36.228.160.137 07/31 11:21

推 smallreader: IF頻寬高要更耗電所以頻寬給很少嗎111.254.174.244 07/31 11:43

推 SHR4587: 下一代移動端應該就是改進延遲問題了 111.241.189.9 07/31 11:46

→ SHR4587: 這次就算有延遲問題整體表現還是很亮眼 111.241.189.9 07/31 11:47

→ SHR4587: 遊戲是可惜了,但會買這類型產品的遊戲 111.241.189.9 07/31 11:47

→ SHR4587: 應該都是附加價值吧 111.241.189.9 07/31 11:47

推 avans: 推解說114.137.200.253 07/31 11:48

推 bunjie: 推詳細解說 111.82.220.142 07/31 11:53

推 Arbin: 遊戲筆電大概還是得要等全大核或是單CCX 111.71.212.194 07/31 12:31

推 oopFoo: 筆電的cpu功耗最重要。現在分成兩個ccx, 36.224.200.235 07/31 12:39

→ oopFoo: 一個是lowish power island,平常就用這個 36.224.200.235 07/31 12:40

→ oopFoo: 高功耗的ccx可以關掉。你串在一起無法關掉 36.224.200.235 07/31 12:41

→ oopFoo: 省電。ringbus很耗電的。上一代的反應不好 36.224.200.235 07/31 12:41

→ oopFoo: 就是功耗降不下來。這個跟MTL的lpe有點像 36.224.200.235 07/31 12:42

→ oopFoo: 但MTL的兩顆ecore太少了。 36.224.200.235 07/31 12:42

推 oopFoo: 以後主流一定是要分流的 36.224.200.235 07/31 12:50

推 smallreader: AMD好像是Mesh但我資訊很久沒更新了111.254.174.244 07/31 13:18

→ smallreader: 哦是在說Intel P/E核同在ringbus耗電111.254.174.244 07/31 13:27

→ higali: 筆電功耗很重要不能像桌面端那樣 219.71.95.18 07/31 13:47

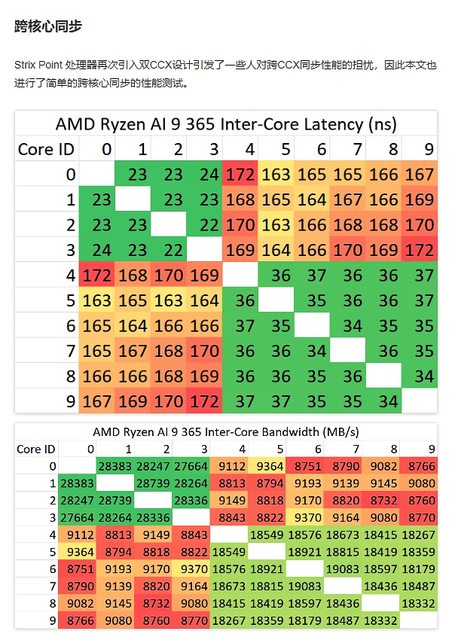

→ pig: anandtech 有把前一代的 latency 拿來做對照218.161.120.232 07/31 14:02

→ pig: 延遲變高,但效能還是把前一代壓在地上打啊218.161.120.232 07/31 14:10

推 SHR4587: 主要是遊戲方面這顆就是夠用就好 111.241.189.9 07/31 14:15

→ SHR4587: 這問題目前看起來就有但不妨礙他是一顆 111.241.189.9 07/31 14:15

→ SHR4587: 很強勁的SOC這樣,下一代能改善是更好 111.241.189.9 07/31 14:16

推 mtc5566: RingBus和Mesh都是Intel的架構 AMD就是CC 118.231.208.21 07/31 14:46

→ mtc5566: X和IF架構 118.231.208.21 07/31 14:46

→ smallreader: 看過說Zen3(?) 8C CCX的拓樸為非全連111.254.174.244 07/31 14:55

→ smallreader: 結的mesh111.254.174.244 07/31 14:55

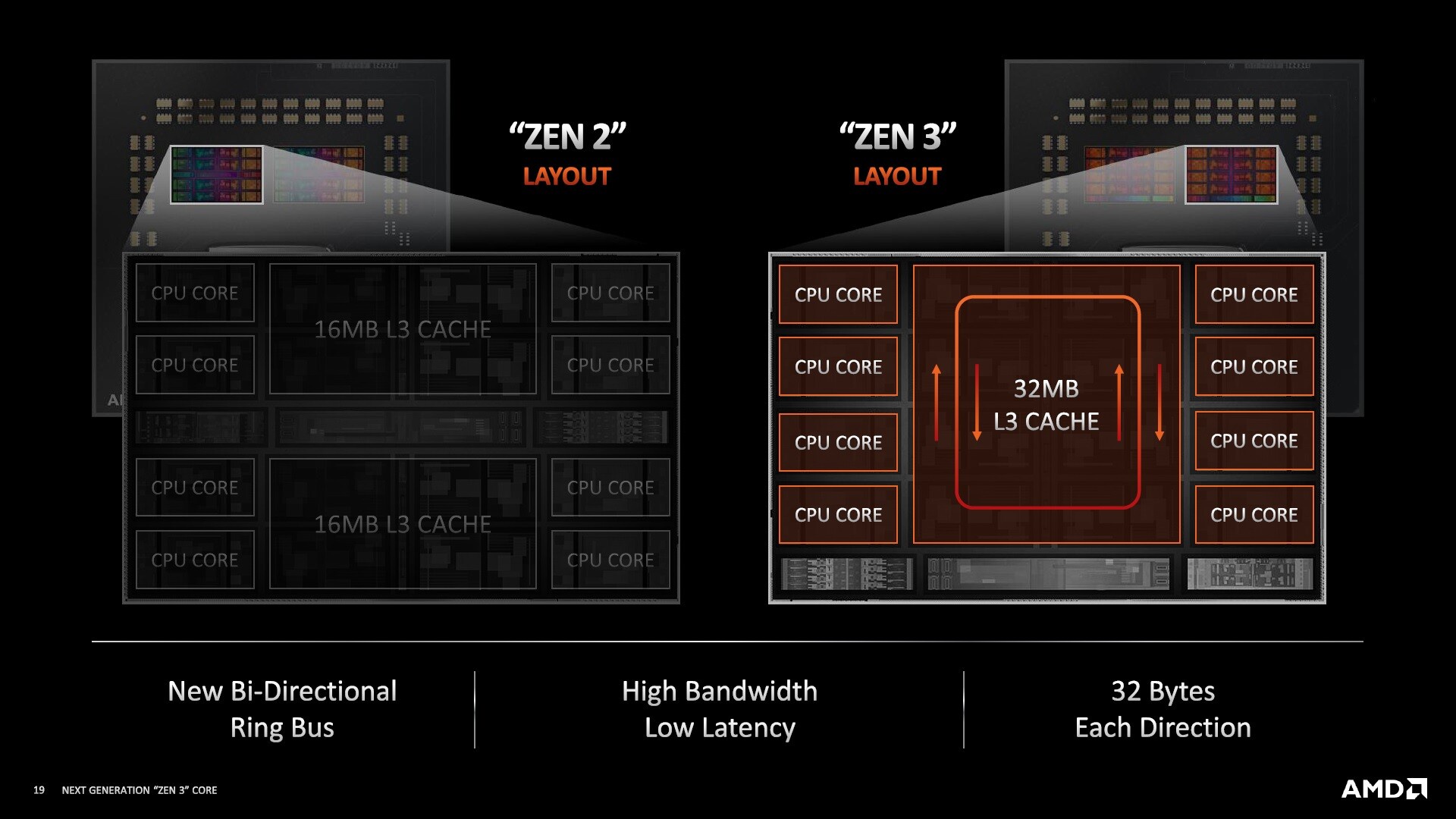

→ oopFoo: Zen3最大的改良就是ringbus。 36.224.200.235 07/31 15:03

推 mayolane: oop又要來懂得都懂了嗎223.136.225.219 07/31 15:04

→ smallreader: 原來是..官方說ring但評測認為非單純111.254.174.244 07/31 15:04

→ smallreader: ring111.254.174.244 07/31 15:04

→ smallreader: 我直接跳成mesh抱歉XD111.254.174.244 07/31 15:04

→ oopFoo: 你那個ring跟cache的ringbus是不同的東西 36.224.200.235 07/31 15:05

→ smallreader: 哦!ring是A-B-C...接力相連 ringbus111.254.174.244 07/31 15:12

→ smallreader: 是地鐵站嗎111.254.174.244 07/31 15:12

推 oppoR20: 最喜歡看兩家粉絲吵架了 兩邊信仰都很純223.139.119.128 07/31 15:15

推 oopFoo: 所以我不想再講了,不是來鬧場,就是真的 36.224.200.235 07/31 15:21

→ oopFoo: 完全不懂。 36.224.200.235 07/31 15:21

→ smallreader: 第10頁,所以正解ring bus XD111.254.174.244 07/31 15:23

推 smallreader: 獻醜了,原來是說AMD L3快取一個環跟111.254.174.244 07/31 15:41

→ smallreader: Intel環上還有IMC,QPI,IO等站 不一樣111.254.174.244 07/31 15:41

→ smallreader: AMD不會為了cross CCX問題去開發12個111.254.174.244 07/31 16:00

→ smallreader: 核的CCX,只有Zen3那次革新 4→8核,111.254.174.244 07/31 16:00

→ smallreader: 要堆核心就用IF連結每個[至多8核]CCX111.254.174.244 07/31 16:00

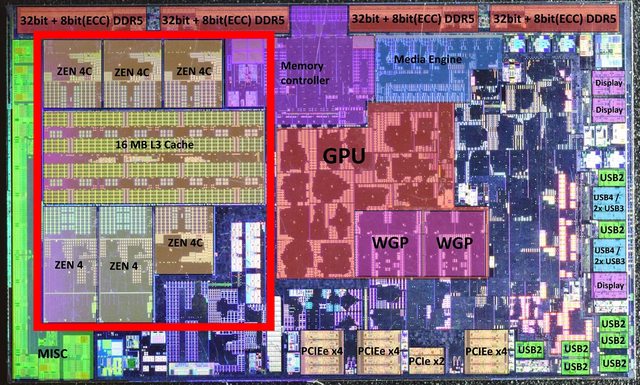

推 smallreader: Phoenix 2 APU那張圖由於是2*Zen4+4*111.254.174.244 07/31 16:04

→ smallreader: Zen4c,6個核所以也能容納一個CCX內111.254.174.244 07/31 16:04

→ smallreader: 16MB可能是拆成大核4MB*2+小核2MB*4111.254.174.244 07/31 16:15

推 sdbb: 羅技無線裝置省電,且有bolt,鍵鼠共用 112.104.64.201 07/31 16:25

→ sdbb: 抱歉推錯篇 112.104.64.201 07/31 16:26

→ smallreader: 查到Bergamo的Zen4c也是每核有2MB L3111.254.174.244 07/31 16:29

→ smallreader: 但Zen5c一個CCX可以上到16核各1MB L3111.254.174.244 07/31 16:29

→ tint: 之前oopFoo網友po的Phoenix2 (Z1)情報 123.204.6.173 07/31 17:01

→ tint: 大小核都在同一個Ring上 共用完整16MB L3 123.204.6.173 07/31 17:02

→ tint: 比如R3 7440U這顆4核心APU 參考AMD官網資料 123.204.6.173 07/31 17:05

→ tint: 只有1個Zen4+3個Zen4c(Phoenix2遮蔽下來的) 123.204.6.173 07/31 17:06

→ tint: L3也進一步砍成4個核心共用8MB L3快取 123.204.6.173 07/31 17:06

→ smallreader: 看↑推文以前猜Zen5c L2會不會減半,111.254.174.244 07/31 17:11

→ smallreader: 現在確定維持1MB,是不是其他細節也111.254.174.244 07/31 17:11

→ smallreader: 跟Zen5一樣,還算是同質核心?111.254.174.244 07/31 17:11

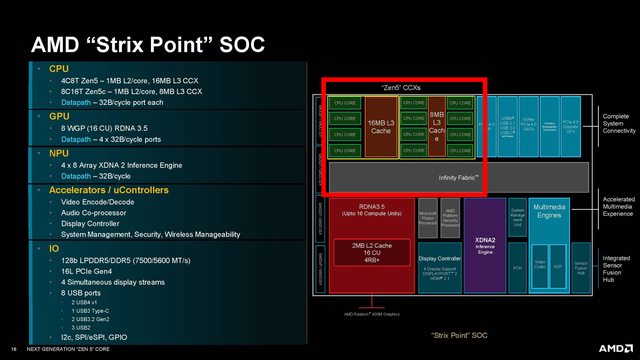

→ tint: 我也覺得這次Strix Point直接採用雙CCX設計 123.204.6.173 07/31 17:13

→ tint: 可能AMD是為了省事 像之前Zen3 Cezanne APU 123.204.6.173 07/31 17:16

推 smallreader: ^看來L3的slice不是一定要4+2*3=10MB111.254.174.244 07/31 17:18

→ smallreader: 因為都在ring上共用 延遲週期也一樣111.254.174.244 07/31 17:18

→ smallreader: 然後遵守2的倍數比較簡單111.254.174.244 07/31 17:18

推 kenny72014a: 如果省電是動態關CCX就猛了 27.240.233.40 07/31 17:20

→ tint: 可能直接從Zen2 Renoir APU的晶片配置上 123.204.6.173 07/31 17:21

→ tint: 替換成Zen3 CPU架構的CCX配置來延續晶片設計 123.204.6.173 07/31 17:23

→ tint: 因為對比Cezanne APU和Renoir APU的Die shot 123.204.6.173 07/31 17:25

→ tint: Zen3 Cezanne的Die上有一塊沒功能的區域 123.204.6.173 07/31 17:25

→ tint: 所以AMD省事省設計也不是一二次了 123.204.6.173 07/31 17:26

推 smallreader: Cezanne從Renoir搬過來 有很多留白處111.254.174.244 07/31 17:27

→ tint: Zen5c更多資訊就看看Kraken Point設計如何了 123.204.6.173 07/31 17:29

→ tint: 畢竟這次Strix Point晶片據說成本不低 123.204.6.173 07/31 17:30

→ tint: Kraken Point可能是更面向主流市場的晶片 123.204.6.173 07/31 17:30

→ tint: 8000G系列下一代桌面版APU 也可能會用Kraken 123.204.6.173 07/31 17:32

→ smallreader: 先猜Kraken Point有2CCX,4個Zen5c的111.254.174.244 07/31 17:35

→ smallreader: CCX砍半剩4MB L3111.254.174.244 07/31 17:35

→ tint: 我覺得Kraken的4個Zen5大核可能仍會精簡L3 123.204.6.173 07/31 17:40

→ tint: 就像過往Zen4、Zen3那樣共用16MB L3的設計 123.204.6.173 07/31 17:41

→ tint: 這樣的設計大小核仍在同一個CCX上機率不低 123.204.6.173 07/31 17:45

→ tint: Kraken APU設計方向可能成本能省則省 123.204.6.173 07/31 17:46

推 smallreader: 了解 而且16MB對任何一個核都是足夠111.254.174.244 07/31 17:48

→ smallreader: 有可能真的精簡化1CCX 16MB111.254.174.244 07/31 17:48

→ smallreader: 甚至測cinebench少掉的L3都不影響XD111.254.174.244 07/31 17:55

推 Windcws9Z: 重點就是比上一代又強又省電 End 59.127.190.36 07/31 18:57

推 oopFoo: Kraken Point不知還會不會出。現在全力在 58.114.66.74 07/31 19:26

→ oopFoo: AI上。Strix其實不錯,4大核8小核是蠻平衡 58.114.66.74 07/31 19:27

→ oopFoo: 的設計。遊戲本來就不是筆電的重點。 58.114.66.74 07/31 19:28

→ justicebb: 拉這麼遠勢必受到物理性質限制,要克123.110.195.144 07/31 21:25

→ justicebb: 服就是增面積跟更耗電更熱123.110.195.144 07/31 21:25

→ friedpig: 再怎麼樣做得比跨die還慢就是有點誇張了 114.32.196.169 08/01 00:17

→ friedpig: 沒chiplet能搞到延遲比過PCB還慢 有點 114.32.196.169 08/01 00:17

→ friedpig: 神奇 114.32.196.169 08/01 00:17

→ mtc5566: 神奇什麼? 啊就為了省電阿 118.231.208.21 08/01 01:44

→ mtc5566: 比較神奇的是延遲低但跑遊戲還是輸的Inte 118.231.208.21 08/01 01:44

→ mtc5566: l 到底幹什麼吃的? 118.231.208.21 08/01 01:44

→ canandmap: 孫燕姿:好~~~~~~神~~~~~~奇~~~~~~~~ 36.228.133.92 08/01 11:17

→ tint: Strix Point這顆如果拿來覆蓋中低階產品 123.204.6.173 08/01 19:21

→ tint: 成本應該是偏高的 中低階需要一顆更小核心 123.204.6.173 08/01 19:23

→ tint: Kraken Point這顆是更精省取向的核心 123.204.6.173 08/01 19:25